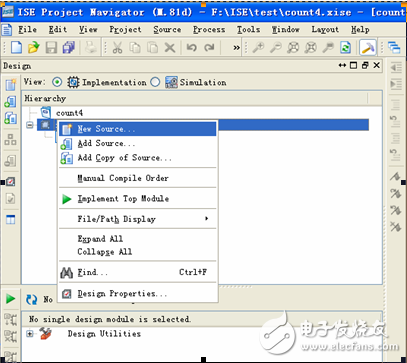

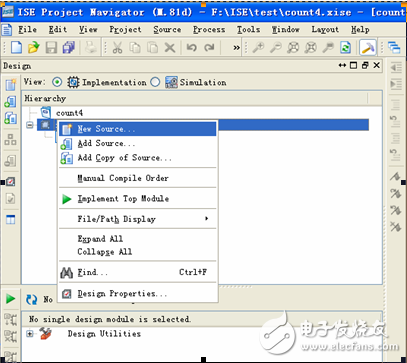

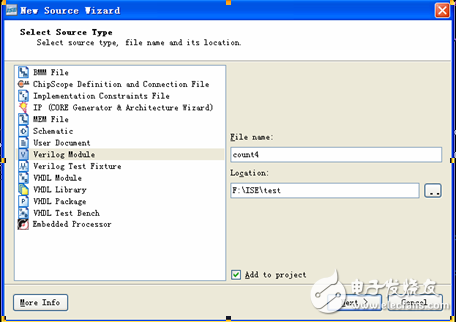

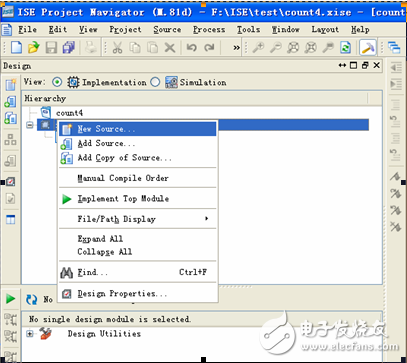

1, code input (1), create a new ISE project, the name is count4. (2), create a new verilog file

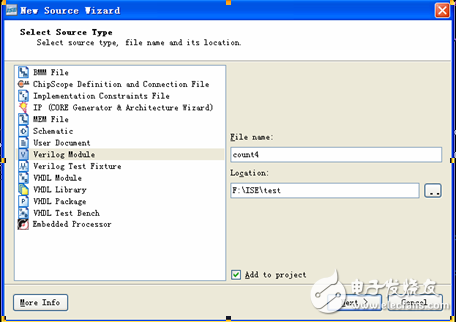

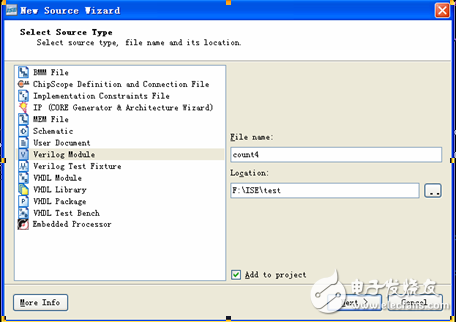

(3), select verilog module Enter file name for count4, click next to know finish.

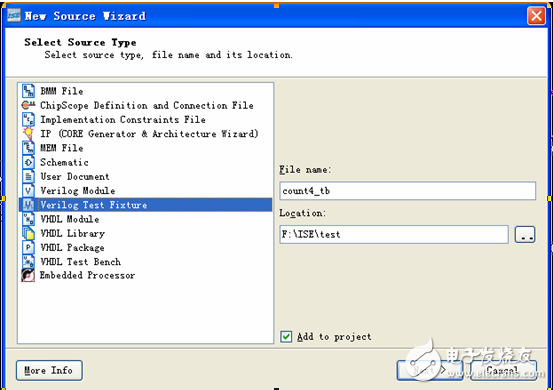

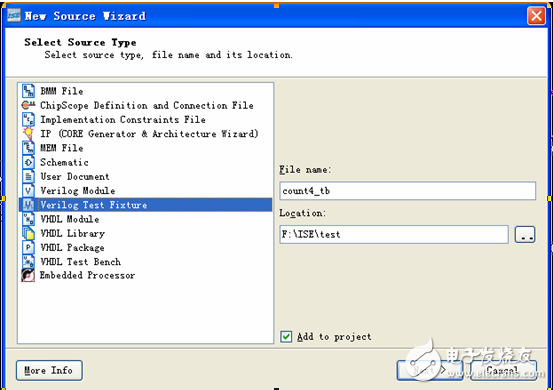

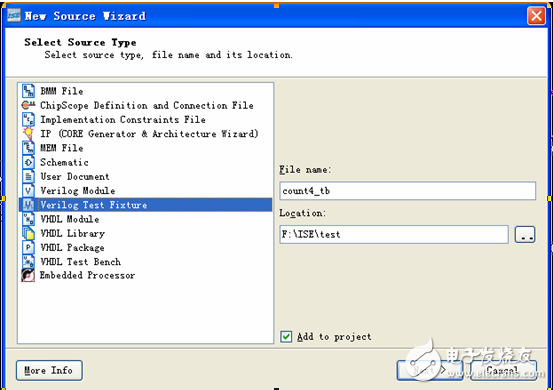

(4) Enter the following code module count4(out,reset,clk) in the count4.v file; output [3:0] out; input reset,clk; reg [3:0] out; always@(posedge clk) Begin if(reset) out<=0; else out<=out+1; endendmodule(5), create a new testbench file (integrated, do not participate in the synthesis), and the same as step (2) (6), select verilog Test Fixture.

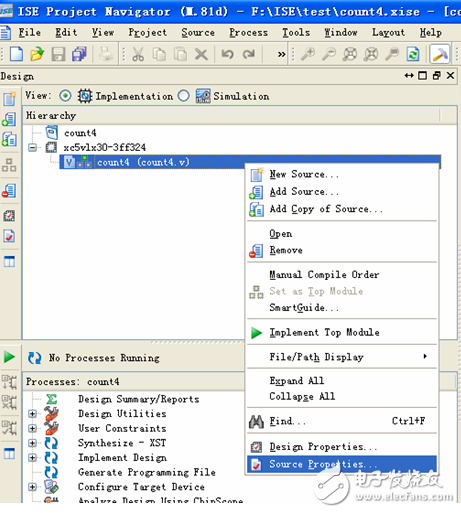

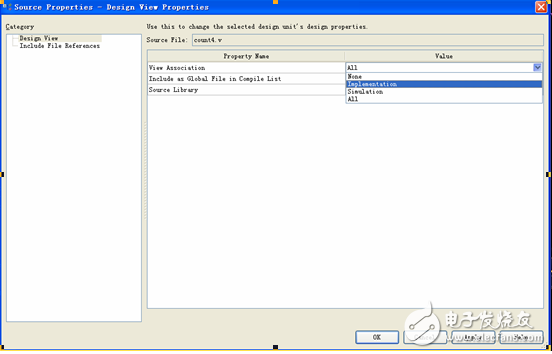

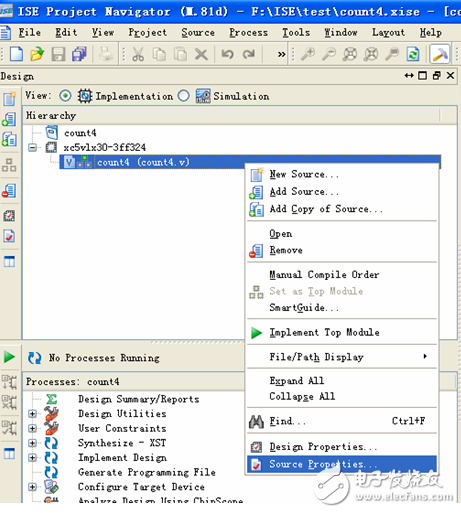

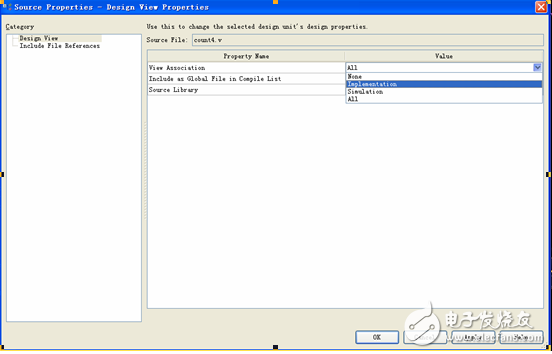

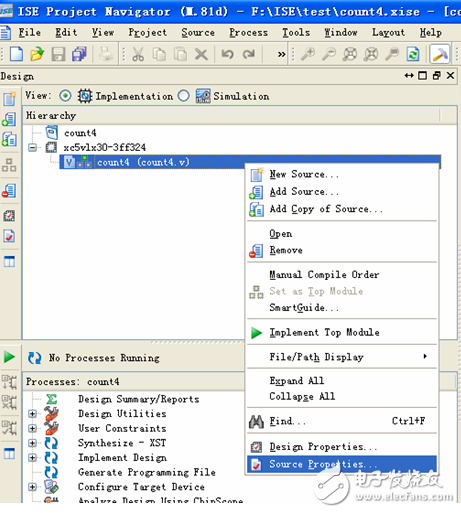

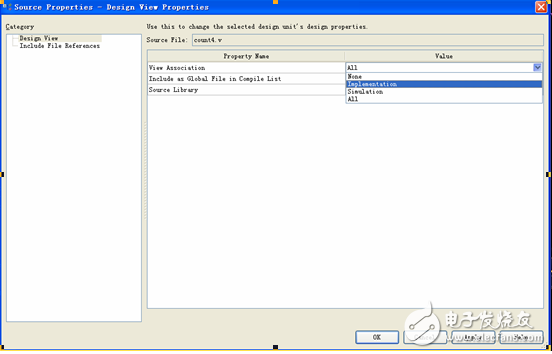

(7) After the creation is complete, enter the following code module count4_tb; reg clk, reset; wire [3:0] out; parameter DELY=100; count4 mycount(.out(out),.reset(reset),.clk( Crk)); //count4 mycount(out,reset,clk); If abbreviated, the function simulation is correct, the timing simulation will be wrong because the port does not match, // will error always #(DELY/2) clk=~clk; iniTIal begin clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*200) $finish; end iniTIal $monitor($TIme,,,"clk=%d reset=%d out=% d",clk,reset,out);endmodule Note: You can modify the file's properties, whether it is testbench or verilog file. Right click on the file you want to modify. Select source properTIes

Modify the properties, simulation for testbench.implementation to normal verilog files

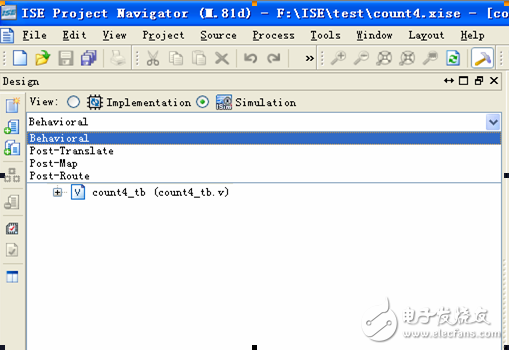

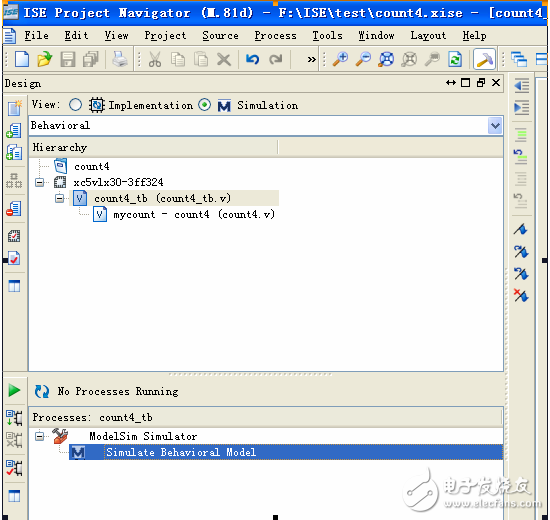

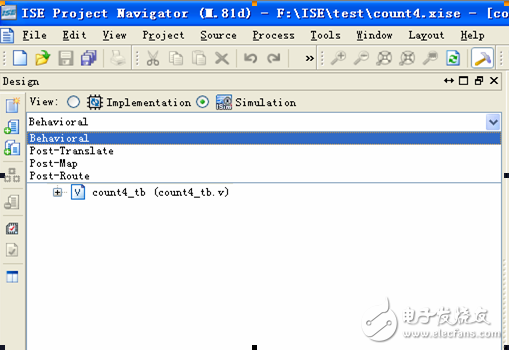

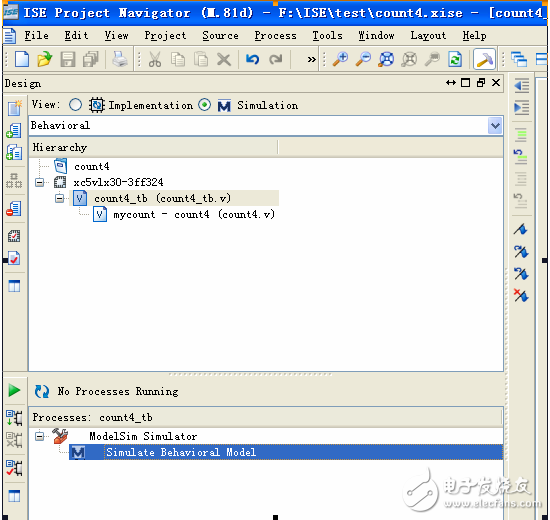

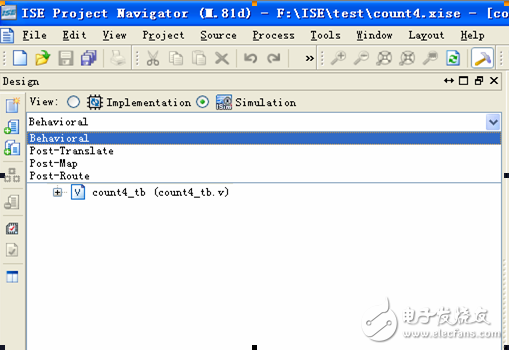

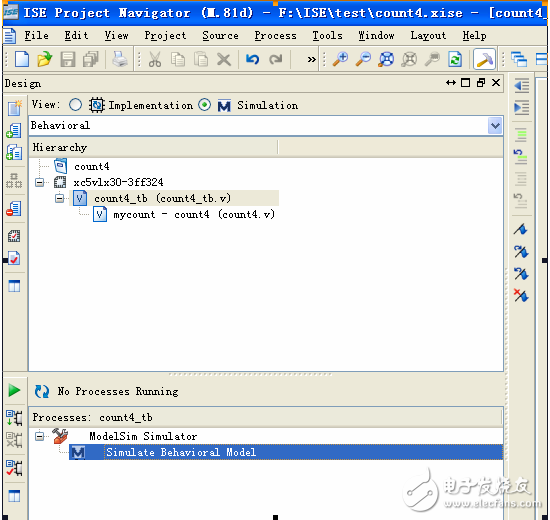

2, functional simulation function simulation is placed in front of the synthesis, because large-scale program synthesis takes a long time, and functional simulation does not need to be integrated, you can first simulate the function to ensure the correctness of the code. After the function simulation is correct, it is integrated, and then the integrated simulation is performed. (1) Switch to simulation. Choose behavioral.

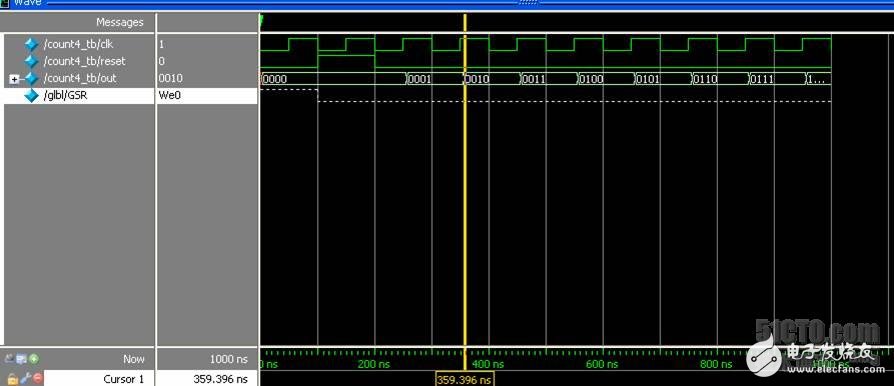

(2) Click to select the count4_tb file, then double-click the simulated behavioral model.

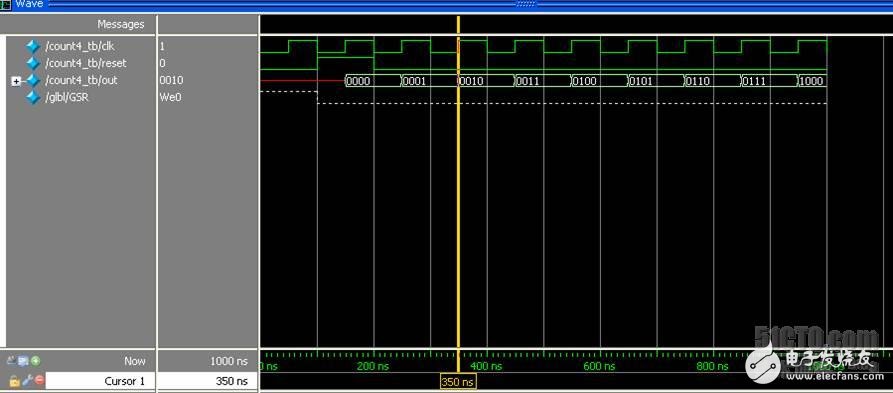

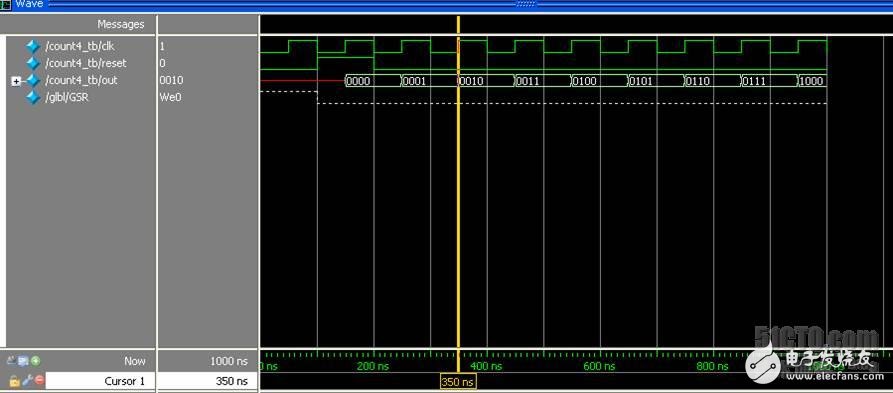

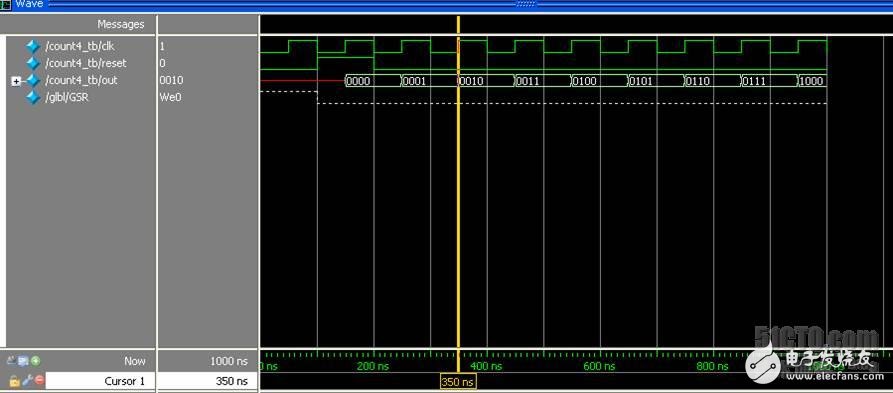

(3) In modelsim, view the waveform and other content.

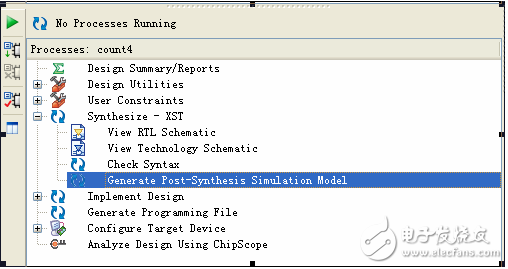

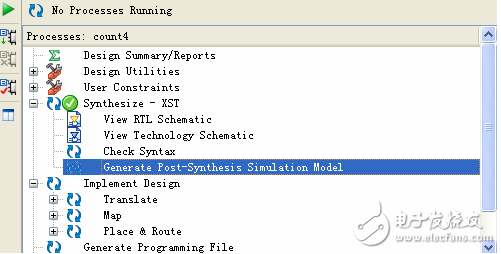

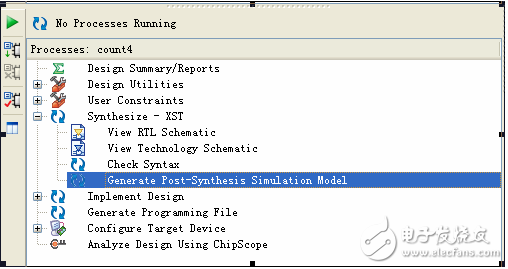

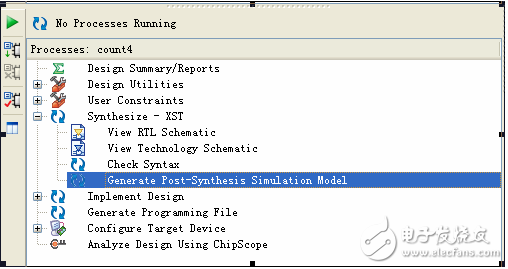

3. Timing (after synthesis) The simulation timing simulation takes into account the delay, including the (and, or,) gate delays generated after integration, as well as the delay caused by the placement and routing. Synthesize is to translate the HDL language design input into a netlist composed of logical units such as AND, OR, NOT, RAM, and flip-flop. After synthesis, a Generate Post-Synthesis Simulation Model can be generated.

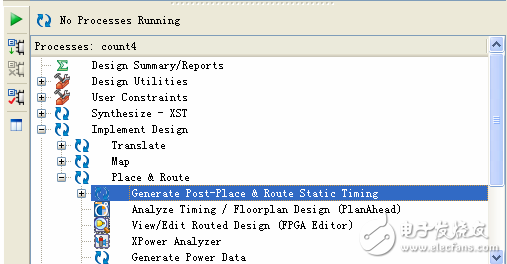

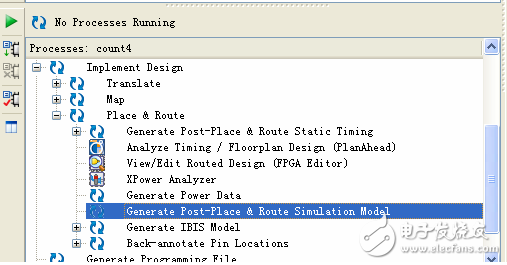

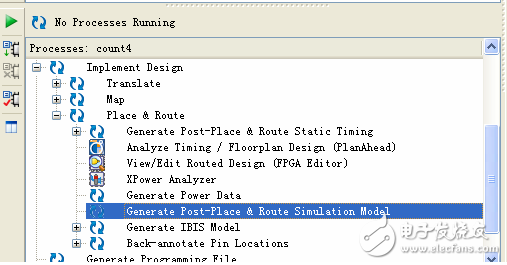

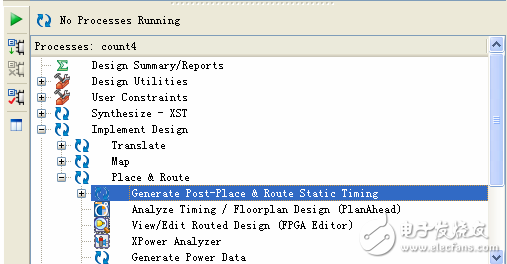

After synthesis, the implementation of ISE (Implement), including translation, mapping, place and route. A simulation model can be generated in all three processes (translation and mapping do not generate delays, so the simulation model generated after the common layout and routing is used for timing simulation)

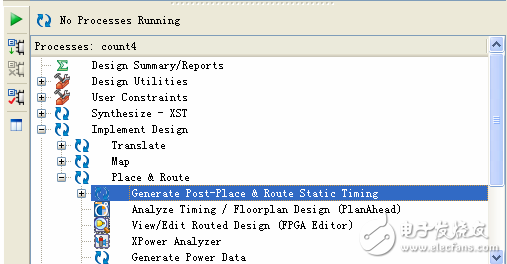

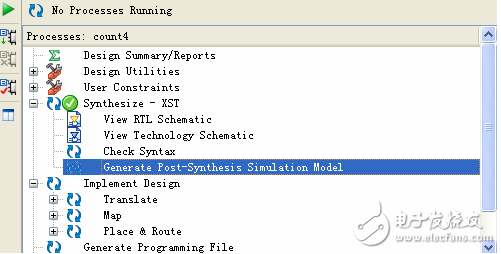

(1), synthesis, double-click Synthesize – XST, want to generate Post-Synthesis Simulation Model, double-click Generate Post-Synthesis Simulation Model, will generate netgen\synthesis\count4_synthesis.v and other files in the project folder

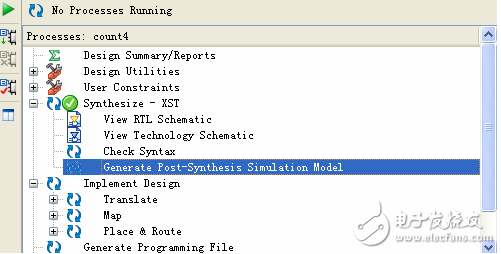

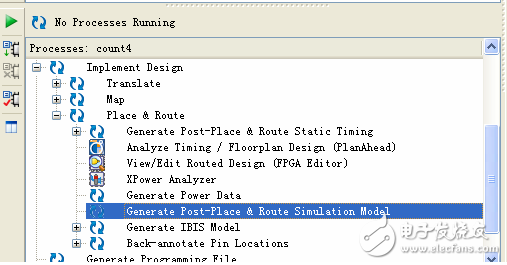

(2) To implement, double-click Implement Design. When finished, double-click Generate Post-Place & Route Simulation Model. Generate a post-layout simulation model.

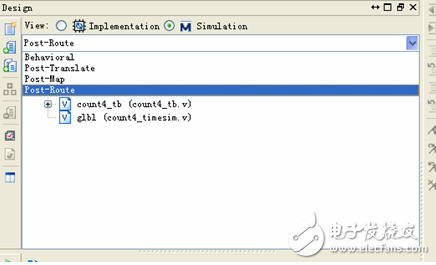

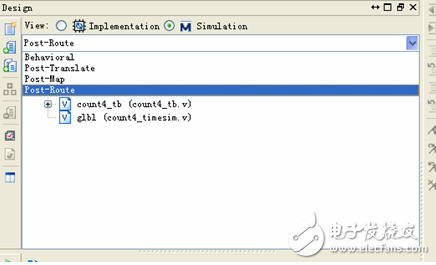

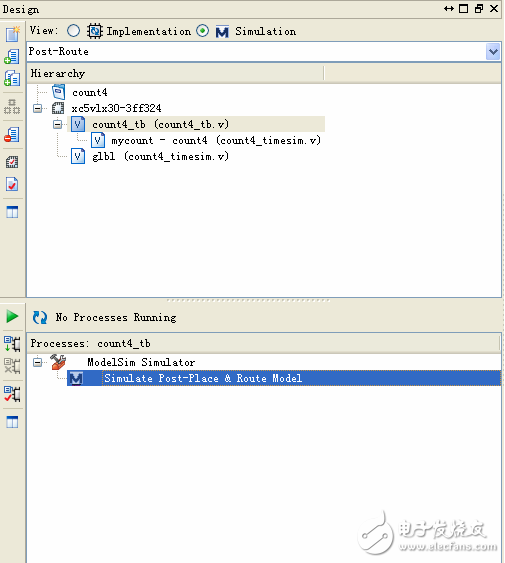

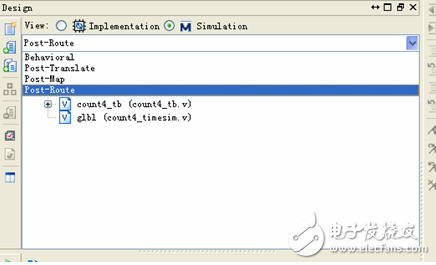

(3), switch to Simulation, select Post-route.

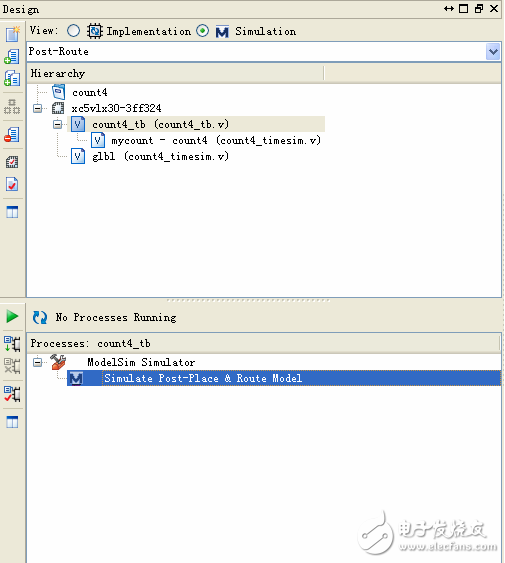

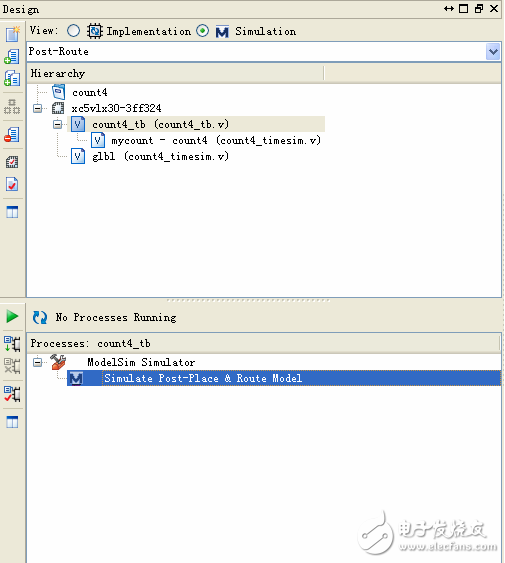

(4), then select the count4_tb file, double-click the following Simulate Post-Place&Route Model to start modelsim.

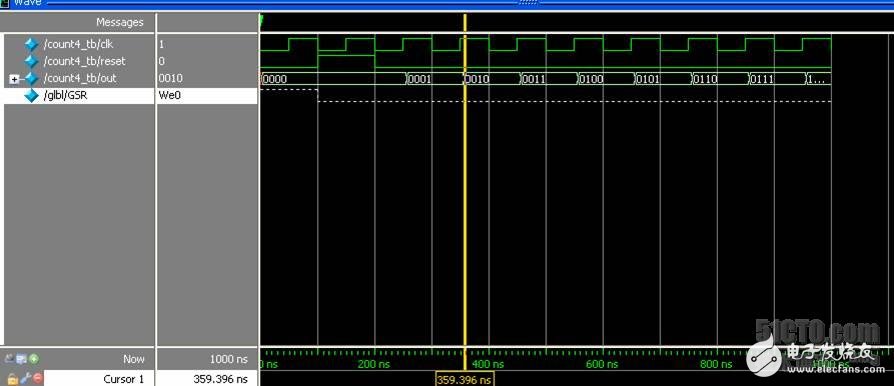

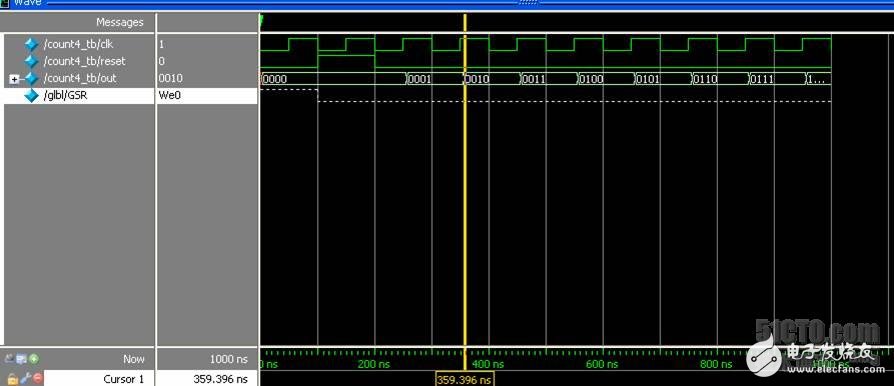

(5) Observe the simulation waveform in modelsim. You can see that the output out has a significant delay.

PET Roll Material

PET Sheet Roll Material,PET Screen Protector Raw Material,PET Raw Material

Guangdong Magic Electronic Limited , https://www.magicmax.cc