eFPGA: A rising star, eFPGA is an embedded FPGA, which is a new type of circuit IP that has recently emerged.

As Moore's Law gets closer to the bottleneck, the cost of making ASIC chips is getting higher and higher. Therefore, designers will want ASICs to achieve some configurability without compromising performance. Among the modules that are expected to be configurable, the interface unit responsible for communicating with other chips or buses bears the brunt. In the chip, communication between modules often uses a simple parallel interface or with simple sequential logic, but in order to ensure reliability during inter-chip communication, the communication interface must be completed through a series of handshake protocols. Designers often want their SoCs to communicate with as many other chips as possible on the market. However, there is no uniform standard for chip communication interfaces on the market, and some communication protocols are also being updated over time, so inter-chip communication is often Need some intermediary chips. In fact, it is common practice to use FPGA chips as an intermediary for inter-chip communication. Because FPGAs are configurable, they can be used as general-purpose communication intermediaries. For example, Apple integrated a small piece of LatTIce FPGA chip in the iPhone7, presumably to achieve inter-chip communication mediation and configurable interconnection. However, the use of additional communication mediation chips in hardware systems is costly and not conducive to maintenance. So, is there a more integrated solution? At this time, eFPGA came into being. By integrating a small FPGA circuit IP into the SoC as an interface handshake protocol processing unit, the flexibility of the SoC interface can be greatly improved, so that it can communicate with other chips.

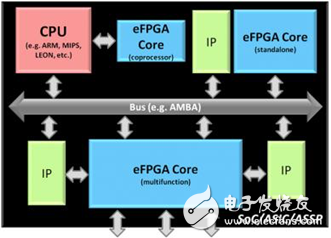

In addition, with the rise of heterogeneous computing architectures, eFPGA has seen a new possibility to achieve highly integrated heterogeneous computing on SoCs, allowing eFPGA to handle different applications as the system demands. Configured as different modules. This is the same as Intel's ultimate goal of acquiring Altera FPGAs. After Intel acquired Altera, Altera's FPGA IP will only be integrated on Intel's chips, and eFPGA vendors can provide IP to any customers who pay for it.

The first eASIC concept to enter the public eye can be said to be published in ISSCC by UCLA's Cheng C. Wang, Fang-Li Yuan and Dejan Markovic, "A MulTI-Granularity FPGA With Hierarchical Interconnects for Efficient and Flexible Mobile CompuTIng". In this article, the authors have solved the problem of the power consumption, performance and cost of the FPGA being limited by the routing resources by creatively designing the interconnection unit, which makes it possible to integrate eASIC into the SoC. Its outstanding contribution won the ISSCC Lewis Award. Later, Cheng C. Wang, Fang-Li Yuan and Dejan Markovic used the results of the paper to set up FlexLogix to promote the concept of eFPGA and make it truly commercial.

This year, the concept of eFPGA has been widely recognized in the industry, and companies in this field are slowly becoming more and more. In the ARM TechCon held a few days ago, we saw four companies, namely FlexLogix, Achronix, QuickLogic and Menta.

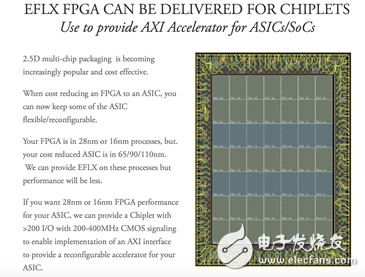

FlexLogix is ​​a pioneer in eFPGA. The new highlight of this year's ARM TechCon is the small FPGA chip for 2.5D package. The main problem solved by this chip is that if the ASIC is implemented using a mature process (such as 65nm), what if the eFPGA does not run as expected at 65nm? Using FlexLogix's small FPGA chip, the 16nm eFPGA and 65nm ASIC can be integrated using 2.5D package technology such as silicon interposer to achieve the system performance required by customers.

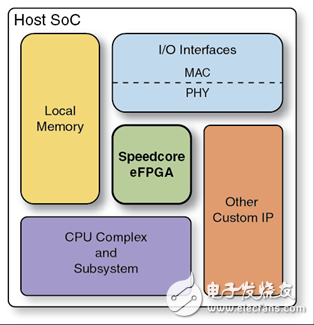

The highlight of Achronix is ​​the high-speed eFPGA IP. Its latest generation of Speedcore IP will be implemented on the TSMC 7nm process for maximum performance. In addition, Achronix's Speedster FPGA chip is also shipping. As the first eFPGA company to enter mass production chips, Achronix's revenue in 2016-2017 has soared, which is worthy of attention.

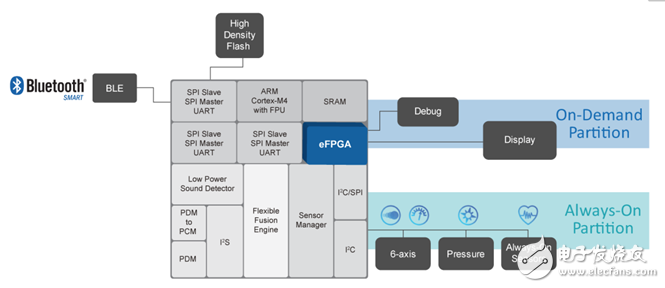

QuickLogic is a veteran FPGA vendor, and now joins the battlefield of eFPGA, bringing us the ArcTIcPro family of IP. Its main market is the ultra-low-power SoC market, such as Bluetooth, the Internet of Things, etc. Its eFPGA will bring configurability to these ultra-low-power SoCs to achieve better power consumption and cost. In addition, QuickLogic's eFPGA supports SMIC, which is known for its cost-effectiveness.

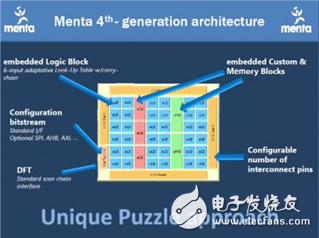

Compared with the previous three, Menta's biggest highlight is the best portability, because the eFPGAs provided by the previous three companies are GDS hard IP, and Menta can provide RTL soft IP, so it can be easily transplanted to different processes.

FPGA SoC: Old Tree Shining

If the eFPGA is to add an FPGA to the SoC, then the concept of the FPGA SoC is to add a processor to the FPGA. After so many years of development, FPGA has become more than just a platform for verifying design, but has become an independent design implementation. The fast reconfigurable nature of the FPGA makes it a platform for many flexibility-demanding platforms.

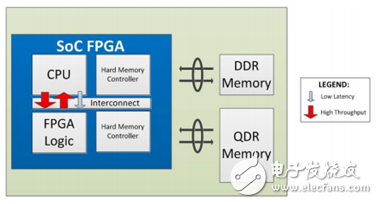

In order to easily control the FPGA from the outside, it is often necessary to implement a microprocessor in the FPGA to run the operating system and related programs, and then efficiently accelerate the part of the program using the configurable logic in the FPGA. Although most of the operations in the program can be accelerated by the FPGA, the operating system part may become the bottleneck of the overall implementation: in traditional FPGAs, the microprocessor is often implemented on the FPGA using a soft core (such as MicroBlaze), so it is better than To speed up the logic, the microprocessor will run slower (clocking frequency "100 MHz"), slowing down the overall system efficiency. In view of this, both Altera and Xilinx have introduced their own solution, which is to integrate a microprocessor hard core (such as ARM series processor) in the FPGA chip. The hard core is implemented without custom FPGAs and therefore runs at very high clock frequencies (~1 GHz or higher). Therefore, in an FPGA SoC, processor performance is no longer a bottleneck, enabling the overall system to achieve higher performance.

Both Xilinx and Altera have introduced FPGA SoC related products and have been unanimously recognized by users. However, the future of FPGA SoCs is much more than the FPGA+ high-speed processor hard core. As we all know, the development of FPGA development ecosystem is slow. An important reason is that the learning curve of hardware logic code writing is very steep, which leads developers to stay away from it. In order to reduce developers' learning costs and speed up development, FPGA vendors have introduced high-level synthesis, which can directly translate high-level languages ​​such as C into RTL, which greatly simplifies FPGA hardware development. The FPGA SoC and the advanced synthesis tool can make the whole development process simpler: first, the developer writes the program code that can be run on the traditional ARM in C, and then the advanced synthesis tool converts the part of the code that can be accelerated by the FPGA into RTL and uses it. The FPGA hardware is implemented, and the rest of the code runs on the ARM hard core in the FPGA SoC. This makes high-performance FPGA development very easy and is expected to allow more developers to join the FPGA ecosystem in the future.

eFPGA and FPGA SoC, who will lead the trend of next-generation programmable hardware?

So, who will be more popular in the future, eFPGA IP and FPGA SoC? The author believes that these two kinds of ecology all indicate that SoC is moving toward a configurable trend in the current bottleneck of Moore's Law, but eFPGA is from the perspective of SoC, while FPGA SoC is from the perspective of traditional FPGA. This is somewhat similar to the previous microprocessor. The technology development path of the traditional processor chip provider represented by Intel is processor-oriented, and integrates more multimedia processing units in the processor chip, such as integrated graphics, making the processor Closer to the SoC; the IP provider represented by ARM is to provide the processor IP, and it becomes more convenient to integrate the appropriate processor IP into the ASIC to become a practical SoC. These two kinds of ecology will exist at the same time, and then they may merge together at some intermediate point as the market develops. let us wait and see!

Windshield Cell Phone Mount,Car Windscreen Mobile Phone Holder,Car Windshield Cell Phone Holder,Car Windscreen Cell Phone Holder

Ningbo Luke Automotive Supplies Ltd. , https://www.car-phone-holder.com