With the rapid development of network technology, FC switches pose new challenges to the analysis of network protocols and the location of faults. Firstly, the working principle of the monitor port (MT) soft core based on the FC switch protocol processing chip is proposed. Then the design and implementation of the monitoring port soft core are carried out. Finally, the functions of the MT port under the virtual simulation platform and the FPGA verification platform are implemented. And performance are simulated and tested separately. The results show that this new intelligent monitoring mode can be used not only for network supervision and troubleshooting, but also for traffic statistics.

The National Standards Committee's X3T11 working group began in 1988 to develop a high-speed serial communication protocol, the Fibre Channel (FC) protocol [1]. In 1997, the Fibre Channel Protocol standard was first introduced at a speed of 1 Gb/s and is now in its sixth generation at 32 Gb/s. Fibre Channel has the advantages of high bandwidth, high reliability, versatility and long connection distance [2]. Fibre Channel is mainly used in two major areas, one is the storage area network, and the other is the avionics environment. At present, domestic and foreign scholars have done a lot of research on the exchange structure and its scheduling algorithm. According to different research methods, the exchange structure scheduling algorithm can be divided into pure theoretical analysis method and fast heuristic scheduling algorithm.

The pure theoretical analysis method mainly discusses the theoretical basis of the scheduling algorithm, such as throughput, delay, and quality of service guarantee. Foreign scholars have proposed the use of high-performance core switching and routers to ensure throughput, speed and latency, and the parallel execution of this algorithm on the input and output ports is scalable [3]. Domestic scholars have proposed a priority real-time scheduling algorithm that guarantees rate [4].

The fast heuristic scheduling algorithm is a scheduling algorithm that is easy to implement in hardware. It is mainly based on its practicability, with small cross-point cache, high efficiency, low complexity, and easy hardware implementation as performance evaluation indicators. CARVAJAL G et al. proposed to add a real-time layer on top of the data link layer to support EDF (Earliest Deadline First) scheduling mechanism. Real-time data packets do not need to be scheduled for transmission in the channel in real time according to the standard of the Ethernet protocol architecture [5].

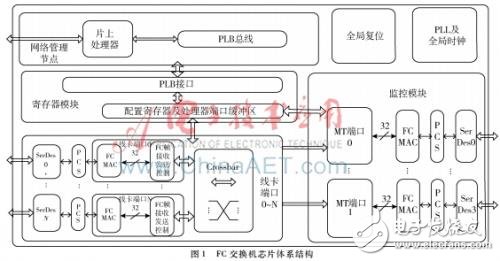

1 FC switch chip architectureThe FC switch chip integrates an embedded on-chip processor to provide data exchange between multi-route card ports and MT ports, and includes on-chip resources such as FC MAC controller and TImer, as well as switch domain ID identification interface and link status indication interface. Full-duplex high-speed serial SerDes interface at multiple speeds. The chip is used in FC switches to complete high-speed uninterrupted switching, data monitoring, communication configuration, clock synchronization and network management functions of the FC network. The FC Fibre Channel switching network can be easily constructed using the chip, and based on this, the Fibre Channel high-speed interconnection between the task subsystems can be quickly realized. The architecture of the FC switch chip is shown in Figure 1.

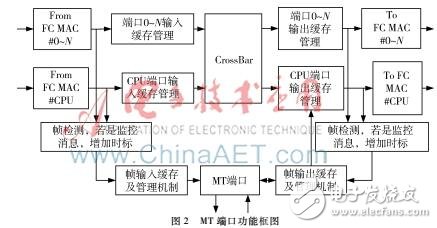

As shown in Figure 2, the monitoring functions of the switch chip include the following aspects:

(1) Support the data function of the monitoring input port;

(2) Support the data function of the monitoring output port;

(3) Support monitoring of data functions containing special field frames; Figure 1 FC switch chip architecture

(4) Supporting frame transmission and reception functions with a network management node (CPU);

(5) Support online dynamic loading of monitoring and routing schemes to complete the corresponding internal register configuration of the chip.

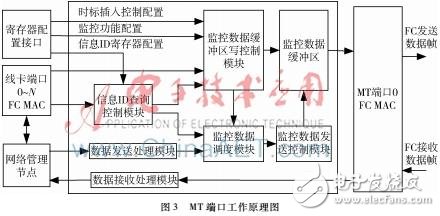

2 FC switch MT port working principleThe FC switch chip MT port module includes the following sub-modules: a monitoring data buffer write control module, an information ID query control module, a monitoring data buffer, a monitoring data scheduling module, a monitoring data transmission control module, a network management node data transmission processing module, and Network management node data receiving processing module. Its working principle is shown as in Fig. 3.

The MT port module is connected to the line card port and the network management node. The MT port can only passively receive data frames from the line card port, and the monitoring mode is divided into input monitoring, output monitoring, and information ID monitoring. The network management node can communicate with the MT port, and the MT port can forward the frame from the network management node or forward the received ELS frame to the network management node. The register configuration sometimes includes functions such as setting settings, monitoring function settings, and information ID buffer configuration.

Motion Control Sensor is an original part that converts the change of non-electricity (such as speed, pressure) into electric quantity. According to the converted non-electricity, it can be divided into pressure sensor, speed sensor, temperature sensor, etc. It is a measurement, control instrument and Parts and accessories of equipment.

Encoder And Decoder,Encoder For Motor , Encoder In Communication,Encoder Communication

Changchun Guangxing Sensing Technology Co.LTD , https://www.gx-encoder.com